### Задание:

- Изучить теорию;

- Написать краткий конспект (таблицы можно распечатать и вложить в конспект);

Результаты работы, фотоотчет, предоставить преподавателю на e-mail: v.vika2014@mail.ru

При возникновении вопросов по приведенному материалу обращаться по следующему номеру телефона: (072)11744922

**ВНИМАНИЕ!!!** При отправке работы, не забывайте указывать ФИО студента, наименование дисциплины, дата проведения занятия (по расписанию).

### Лекция 9

Тема: Логические узлы ЭВМ и их классификация. Сумматоры, дешифраторы, программируемые логические матрицы, их назначение и применение.

## Основные вопросы:

Классификация элементов и узлов ЭВМ Комбинационные схемы Дешифраторы и шифраторы

# Классификация элементов и узлов ЭВМ

При рассмотрении структуры любой ЭВМ обычно проводят ее детализацию. Как правило, в структуре ЭВМ выделяют следующие структурные единицы:

- устройства,

- узлы,

- блоки и

- элементы.

Такая детализация соответствует вполне определенным операциям преобразования информации, заложенным в программах пользователей.

Нижний уровень обработки реализуют элементы. Каждый элемент предназначается для обработки единичных электрических сигналов, соответствующих битам информации.

**Узлы** обеспечивают одновременную обработку группы сигналов информационных слов.

**Блоки** реализуют некоторую последовательность в обработке информационных слов — функционально обособленную часть машинных операций (блок выборки команд, блок записи-чтения и др.).

*Устройства* предназначаются для выполнения отдельных машинных операций и их последовательностей (АЛУ, УУ...).

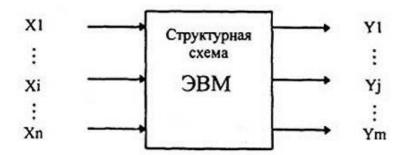

В общем случае любая структурная единица ЭВМ обеспечивает преобразование входной информации X в выходную У (см. рис.1).

Рис. 1. Представление схемы ЭВМ

В этом случае зависимостями  $y_j = f(x_1, x_2, ..., x_i, ..., x_n)$ , где  $x_i - i$ -й вход; n — число входов;  $y_i - i$ -й выход; m — число выходов в устройстве, можно описывать алгоритм работы любого устройства ЭВМ.

Все современные вычислительные машины строятся на комплексах (системах) **интегральных микросхем (ИС).** Электронная микросхема называется **интегральной**, если ее компоненты и соединения между ними выполнены

- в едином технологическом цикле,

- на едином основании и

- имеют общую герметизацию и защиту от механических воздействий.

Каждая микросхема представляет собой миниатюрную электронную схему, сформированную послойно в кристалле полупроводника: кремния, германия, арсениде галлия и т.д. В состав микропроцессорных наборов включаются различные типы микросхем, но все они должны иметь единый тип межмодульных связей, основанный на стандартизации параметров сигналов взаимодействия (амплитуда, полярность, длительность импульсов и т.п.). Основу набора обычно составляют большие ИС (БИС) и даже сверхбольшие интегральные схемы (СБИС). На очереди следует ожидать появления ультра больших ИС (УБИС). Кроме них обычно используются микросхемы с малой и средней степенью интеграции (СИС).

Функционально **микросхемы** могут соответствовать **устройству, узлу или блоку**, но каждая из них состоит из комбинации простейших **логических элементов**, реализующих функции формирования, преобразования, запоминания сигналов и т.д.

Элементы ЭВМ можно классифицировать по различным признакам. Наиболее часто такими признаками являются:

- тип сигналов,

- назначение элементов,

- технология их изготовления и т.д.

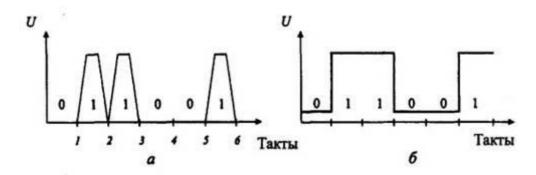

В ЭВМ широко применяют два способа физического представления сигналов: *импульсный и потенциальный*. При *импульсном* способе представления сигналов единичному значению некоторой двоичной переменной ставится в соответствие наличие импульса (тока или напряжения), нулевому значению — отсутствие импульса (рис. 2.,*a*). Длительность импульсного сигнала не превышает один такт синхроимпульсов.

При *потенциальном или статическом* представлении сигналов единично значение двоичной переменной отображается высоким уровнем напряжения, а нулевое

Рис. 2. Представление информации в ЭВМ: a — импульсные сигналы;  $\delta$  — потенциальные сигналы

Независимо от вида сигналов различают *последовательный и параллельныйкоды* передачи и представления информации в ЭВМ.

При *последовательном коде* представления данных используются одиночные шины или линии передачи, в которых сигналы, соответствующие отдельным разрядам данных, разнесены во времени. Обработка такой информации производится последовательно разряд за разрядом. Такой вид представления и передачи данных требует весьма экономичных по аппаратурным затратам схем обработки данных. Время же обработки определяется числом обрабатываемых сигналов (разрядов).

**Параллельный код** отображения и передачи информации предполагает параллельную и одновременную фиксацию всех разрядов данных на различных шинах, т.е. параллельный код данных развернут в пространстве. Это дает возможность ускорить обработку во времени, но затраты на аппаратурные средства при этом возрастают пропорционально числу обрабатываемых разрядов.

Во всех вычислительных машинах используются и *параллельно-последовательные коды* представления информации. При этом информация отображается частями. Части поступают на обработку последовательно, а каждая часть данных представляется параллельным кодом.

По своему назначению элементы делятся на:

- формирующие,

- логические и

- запоминающие.

К формирующим элементам относятся различные формирователи, усилители, усилители-формирователи и т.п. Данные элементы служат для выработки определенных электрических сигналов, восстановления их параметров (амплитуды, полярности, мощности, длительности).

В каждой ЭВМ имеются специальные блоки, формирующие сигналы тактовой частоты, серии синхронизирующих и управляющих сигналов, координирующих работу всех схем ЭВМ. Интервал времени между импульсами основной частоты называется тактом. Длительность такта является важной характеристикой ЭВМ, определяющей ее потенциальную производительность. Время выполнения любой операции ЭВМ связано с определенным числом тактов.

Простейшие *погические элементы* преобразуют входные сигналы в соответствии с элементарными логическими функциями, рассмотренными ранее. В свою очередь, полученные сигналы могут формировать следующий уровень сигналов и т. д. Сложные

преобразования в соответствии с требуемыми логическими зависимостями могут приводить к построению многоуровневых схем. Каждая такая схема представляет собой композицию простейших логических схем.

Запоминающим элементом называется элемент, который способен принимать и хранить код двоичной цифры (единицы или нуля). Элементы памяти могут запоминать и сохранять исходные значения некоторых величин, промежуточные значения обработки и окончательные результаты вычислений. Только запоминающие элементы в схемах ЭВМ позволяют проводить обработку информации с учетом ее развития.

### Комбинационные схемы

Обработка входной информации X в выходную Y (см. рис. 6.1) в любых схемах ЭВМ обеспечивается преобразователями или цифровыми автоматами двух видов: комбинационными схемами и схемами с памятью.

*Комбинационные схемы (КС)* — это схемы, у которых выходные сигналы Y

$=(y_1, y_2, ..., y_m)$  в любой момент дискретного времени однозначно определяются совокупностью входных сигналов  $X=(x_1, x_2,..., x_n)$ , поступающих в тот же момент времени t. Реализуемый в КС способ обработки информации называется комбинационным потому, что результат обработки зависит только от комбинации входных сигналов и формируется сразу при поступлении входных сигналов. Поэтому одним из достоинств комбинационных схем является их высокое быстродействие. Преобразование информации однозначно описывается логическими функциями вида Y=f(X).

Логические функции и соответствующие им комбинационные схемы подразделяют на

- регулярные и

- нерегулярные структуры.

**Регулярные структуры** предполагают построение схемы таким образом, что каждый из ее выходов строится по аналогии с предыдущими. В **нерегулярных структурах** такая аналогия отсутствует. Примером построения нерегулярной структуры может служить разработка схемы в примере схемы, фиксирующей появление "неправильной" тетрады в двоично-десятичном представлении чисел (см. предыдущую лекцию).

В практике проектирования ЭВМ накоплен огромный опыт по синтезу различных схем. Многие регулярные структуры положены в основу построения отдельных ИС малой и средней степени интеграции или отдельных функциональных частей БИС и СБИС. Из регулярных комбинационных схем наиболее распространены дешифраторы, шифраторы, схемы сравнения, комбинационные сумматоры, коммутаторы и др.

Рассмотрим принципы построения подобных регулярных структур.

## Дешифраторы и шифраторы

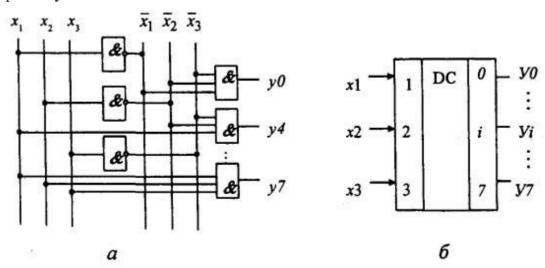

**Дешифраторы** (ДШ) — это комбинационные схемы с n входами и  $m=2^n$  выходами. Единичный сигнал, формирующийся на одном из m выходов, однозначно соответствует комбинации входных сигналов.

Например, разработка структуры ДШ для n=3 позволяет получить таблицу истинности (табл. 1) и логические зависимости.

Таблица 1 - Таблица истинности дешифратора

|       | Входь | I     | Выходы |                |       |     |       |  |  |

|-------|-------|-------|--------|----------------|-------|-----|-------|--|--|

| $x_1$ | $x_2$ | $x_3$ | $Y_0$  | Y <sub>1</sub> | $Y_5$ | ••• | $Y_7$ |  |  |

| 0     | 0     | 0     | 1      | 0              | 0     |     | 0     |  |  |

| 0     | 0     | 1     | 0      | 1              | 0     |     | 0     |  |  |

| 0     | 1     | 0     | 0      | 0              | 0     |     | 0     |  |  |

| 0     | 1     | 1     | 0      | 0              | 0     | ••• | 0     |  |  |

| 1     | 0     | 0     | 0      | 0              | 0     |     | 0     |  |  |

| 1     | 0     | 1     | 0      | 0              | 1     |     | 0     |  |  |

| 1     | 1     | 0     | 0      | 0              | 0     |     | 0     |  |  |

| 1     | 1     | 1     | 0      | 0              | 0     |     | 1     |  |  |

Дешифраторы широко используются в ЭВМ для выбора информации по определенному адресу, для расшифровки кода операции и др. Логические зависимости дешифратора:

$$y_0 = \bar{x}_1 \bar{x}_2 \bar{x}_3, \quad y_4 = x_1 \bar{x}_2 \bar{x}_3,$$

$y_1 = \bar{x}_1 \bar{x}_2 x_3, \quad y_5 = x_1 \bar{x}_2 x_3,$

$y_2 = \bar{x}_1 x_2 \bar{x}_3, \quad y_6 = x_1 x_2 \bar{x}_3,$

$y_3 = \bar{x}_1 x_2 x_3, \quad y_7 = x_1 x_2 x_3.$

На рис. 3 представлены структурная схема ДШ, построенная в базисе (**И**, **HE**), и условное ее обозначение на принципиальных электрических схемах ЭВМ. Кружочки у линий, выходящих из логических элементов, указывают на инверсию функций, реализуемых элементами.

Рис. 3. Структурная схема дешифратора *(а)* и обозначение дешифратора на принципиальных электрических схемах (б)

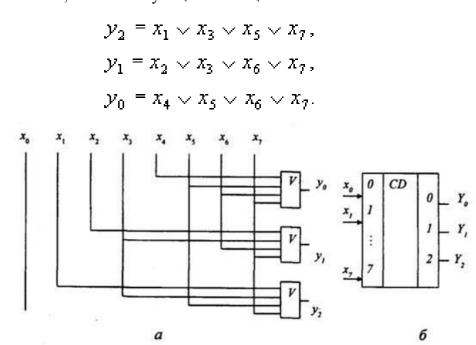

**Шифрамор** (ШР) решает задачу, обратную схемам ДШ, т. е. по номеру входного сигнала формирует однозначную комбинацию выходных сигналов. Рассмотрим пример построения ШР, который иллюстрируется таблицей истинности 2 и схемами на рис. 4.

Таблица 2 - Таблица истинности шифратора

|       |                       | Входы      |            |            |            | Выходы     |    |            |            |

|-------|-----------------------|------------|------------|------------|------------|------------|----|------------|------------|

| $x_1$ | <i>x</i> <sub>2</sub> | <b>x</b> 3 | <i>x</i> 4 | <i>x</i> 5 | <b>x</b> 6 | <i>x</i> 7 | yo | <b>y</b> 1 | <b>y</b> 2 |

| 1     | 0                     | 0          | 0          | 0          | 0          | 0          | 0  | 0          | 1          |

| 0     | 1                     | 0          | 0          | 0          | 0          | 0          | 0  | 1          | 0          |

| 0     | 0                     | 1          | 0          | 0          | 0          | 0          | 0  | 1          | 1          |

| 0     | 0                     | 0          | 1          | 0          | 0          | 0          | 1  | 0          | 0          |

| 0     | 0                     | 0          | 0          | 1          | 0          | 0          | 1  | 0          | 1          |

| 0     | 0                     | 0          | 0          | 0          | 1          | 0          | 1  | 1          | 0          |

| 0     | 0                     | 0          | 0          | 0          | 0          | 1          | 1  | 1          | 1          |

Логические зависимости, соответствующие таблице истинности:

Рис. 4. Структурная схема шифратора *(а)* и обозначение шифратора напринципиальных электрических схемах (б)

Обратим внимание, что таблицы 1 и 2 во многом похожи: входы и выходы в них поменялись местами. Состояния входов табл. 2. содержат только по одному единичному элементу. Другие произвольные комбинации входов недопустимы.